Digital Signal Processing: Laboratory Experiments Using C and the TMS320C31 DSK Rulph Chassaing Copyright © 1999 John Wiley & Sons, Inc. Print ISBN 0-471-29362-8 Electronic ISBN 0-471-20065-4

**Digital Signal Processing**

#### WILEY SERIES ON TOPICS IN DIGITAL SIGNAL PROCESSING

- DFT/FFT and Convolution Algorithms and Implementation *by* C. S. Burrus and T. W. Parks

- Digital Signal Processing: Laboratory Experiments Using C and the TMS320C31 DSK *by* Rulph Chassaing

- Digital Signal Processing with the TMS320C25 *by* Rulph Chassaing and Darrell W. Horning

- A Simple Approach to Digital Signal Processing by Craig Marven and Gillian Ewers

- Digital Filter Design *by* T. W. Parks and C. S. Burrus

- Theory and Design of Adaptive Filters *by* John R. Treichler and C. Richard Johnson

# **Digital Signal Processing**

Laboratory Experiments Using C and the TMS320C31 DSK

**RULPH CHASSAING**

University of Massachusetts, Dartmouth

A Wiley-Interscience Publication JOHN WILEY & SONS, INC. New York • Chichester • Weinheim • Brisbane • Singapore • Toronto Designations used by companies to distinguish their products are often claimed as trademarks. In all instances where John Wiley & Sons, Inc., is aware of a claim, the product names appear in initial capital or ALL CAPITAL LETTERS. Readers, however, should contact the appropriate companies for more complete information regarding trademarks and registration.

Copyright © 1999 by John Wiley & Sons, Inc. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic or mechanical, including uploading, downloading, printing, decompiling, recording or otherwise, except as permitted under Sections 107 or 108 of the 1976 United States Copyright Act, without the prior written permission of the Publisher. Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Inc., 605 Third Avenue, New York, NY 10158-0012, (212) 850-6011, fax (212) 850-6008, E-Mail: PERMREQ @ WILEY.COM.

This publication is designed to provide accurate and authoritative information in regard to the subject matter covered. It is sold with the understanding that the publisher is not engaged in rendering professional services. If professional advice or other expert assistance is required, the services of a competent professional person should be sought.

ISBN 0-471-20065-4.

This title is also available in print as ISBN 0-471-29362-8.

For more information about Wiley products, visit our web site at www.Wiley.com.

### Contents

| Pr | eface   |                                                            | ix   |

|----|---------|------------------------------------------------------------|------|

| Li | st of H | Examples                                                   | xiii |

| Li | st of I | Programs/Files on Accompanying Disk                        | XV   |

| 1  | DIG     | ITAL SIGNAL PROCESSING DEVELOPMENT SYSTEM                  | 1    |

|    | 1.1     | Introduction                                               | 1    |

|    | 1.2     | DSK Support Tools                                          | 2    |

|    | 1.3     | Programming Examples to Test the DSK Tools                 | 3    |

|    | 1.4     | Additional Support Tools                                   | 14   |

|    | 1.5     | Experiment 1: Testing the DSK Tools                        | 16   |

|    | Refe    | erences                                                    | 17   |

| 2  |         | CHITECTURE AND INSTRUCTION SET OF THE<br>S320C3x PROCESSOR | 19   |

|    | 2.1     | Introduction                                               | 19   |

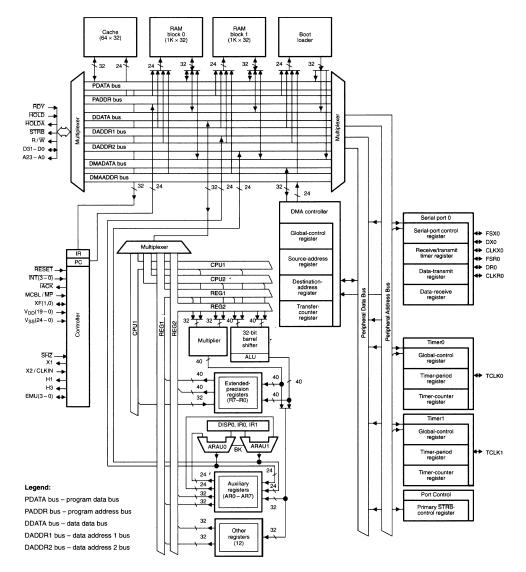

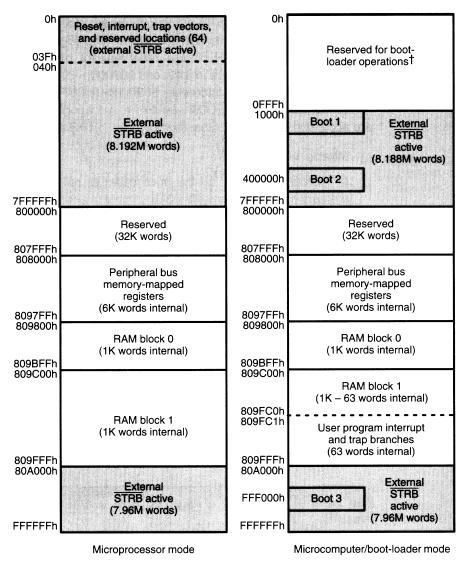

|    | 2.2     | TMS320C3x Architecture and Memory Organization             | 21   |

|    | 2.3     | Addressing Modes                                           | 25   |

|    | 2.4     | TMS320C3x Instruction Set                                  | 26   |

|    | 2.5     | Assembler Directives                                       | 30   |

|    | 2.6     | Other Considerations                                       | 32   |

|    | 2.7     | Programming Examples Using TMS320C3x and C code            | 34   |

|    | 2.8     | Experiment 2: TMS320C3x Instructions and Associated Tools  | 47   |

|    | Refe    | erences                                                    | 48   |

| 3  | INP     | UT AND OUTPUT WITH THE DSK                                 | 51   |

|    | 3.1     | Introduction                                               | 51   |

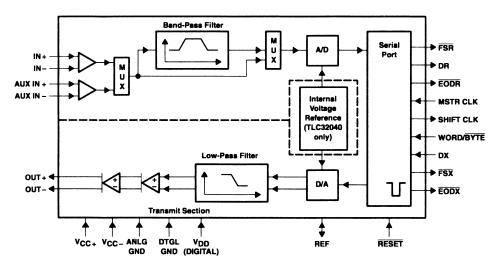

|    | 3.2     | The Analog Interface Circuit (AIC) Chip                    | 53   |

|    |         |                                                            | v    |

|   | 3.3        | Interrupts and Peripherals                                                                          | 59         |

|---|------------|-----------------------------------------------------------------------------------------------------|------------|

|   | 3.4        | Programming Examples Using TMS320C3x and C code                                                     | 60         |

|   | 3.5        | PC Host - TMS320C31 Communication                                                                   | 80         |

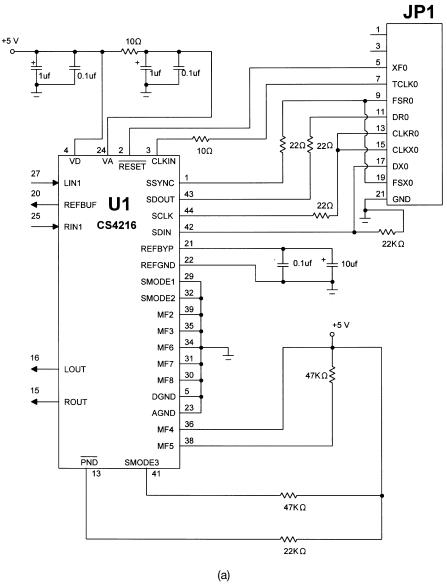

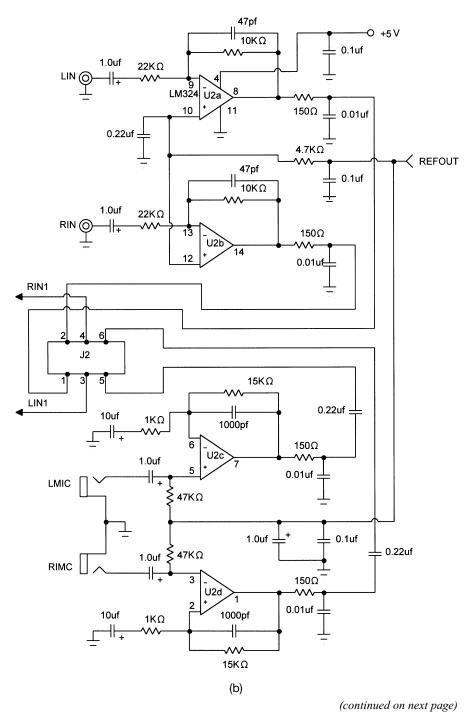

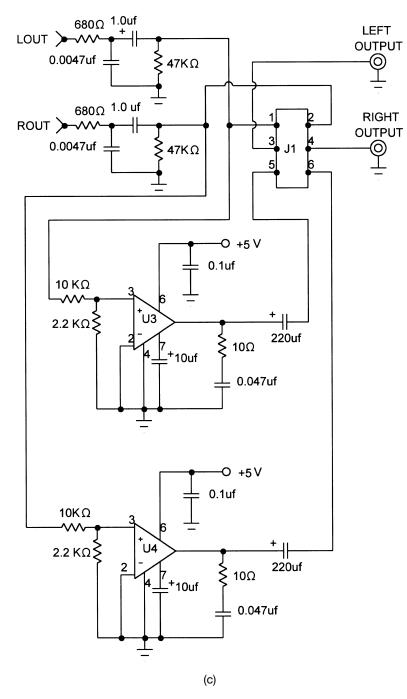

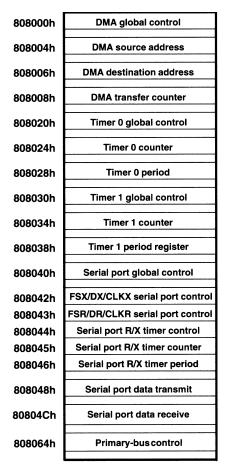

|   | 3.6        | External/Flash Memory and I/O with 16-bit Stereo Audio Codec                                        | 87         |

|   | 3.7        | Experiment 3: Input and Output with the DSK                                                         | 88         |

|   | Refe       | prences                                                                                             | 89         |

| 4 | FIN        | ITE IMPULSE RESPONSE FILTERS                                                                        | 91         |

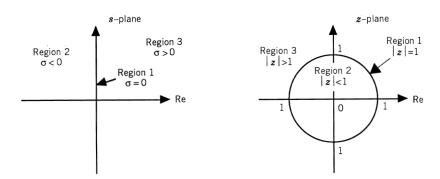

|   | 4.1        | Introduction to the z-Transform                                                                     | 91         |

|   | 4.2        | Discrete Signals                                                                                    | 96         |

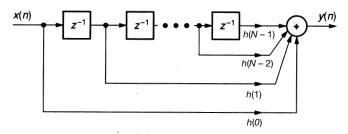

|   | 4.3        | Finite Impulse Response Filters                                                                     | 97         |

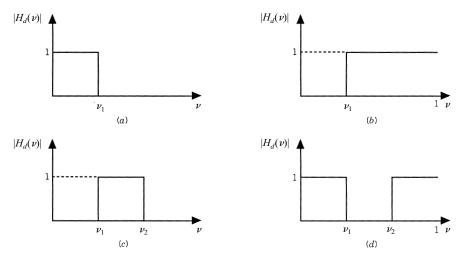

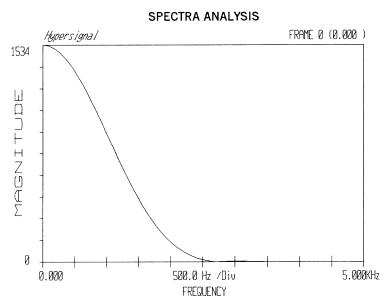

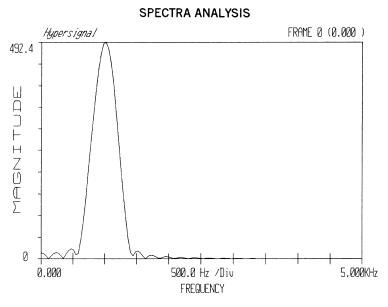

|   | 4.4        | FIR Implementation Using Fourier Series                                                             | 99         |

|   | 4.5        | Window Functions                                                                                    | 103        |

|   | 4.6        | Filter Design Packages                                                                              | 106        |

|   | 4.7        | Programming Examples using TMS320C3x and C Code                                                     | 106        |

|   | 4.8        | Experiment 4: FIR Filter Implementation                                                             | 129        |

|   | Refe       | prences                                                                                             | 131        |

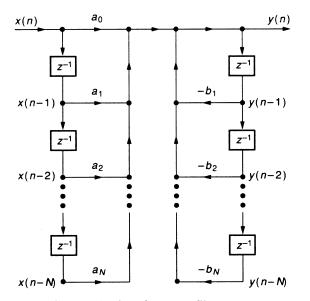

| 5 | INF        | INITE IMPULSE RESPONSE FILTERS                                                                      | 135        |

|   | 5.1        | Introduction                                                                                        | 135        |

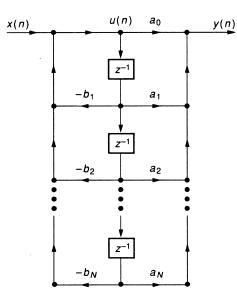

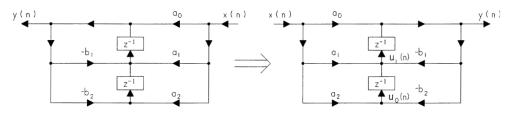

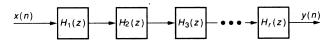

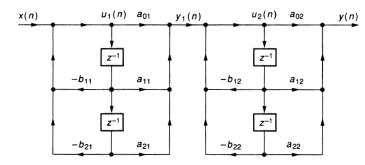

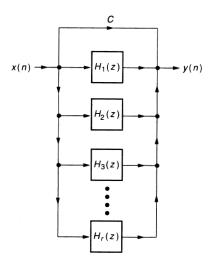

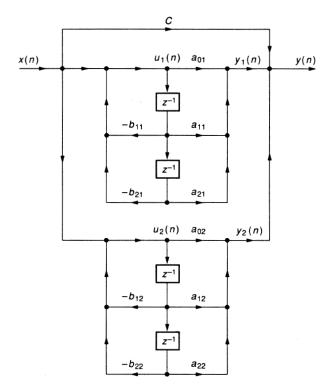

|   | 5.2        | IIR Filter Structures                                                                               | 136        |

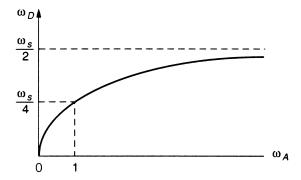

|   | 5.3        | Bilinear Transformation                                                                             | 143        |

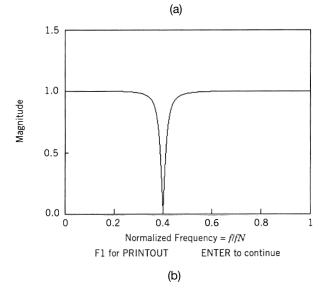

|   | 5.4        | Programming Examples Using TMS320C3x and C Code                                                     | 150        |

|   | 5.5        | Experiment 5: IIR Filter Design and Implementation                                                  | 160        |

|   | Refe       | prences                                                                                             | 163        |

| 6 | FAS        | T FOURIER TRANSFORM                                                                                 | 165        |

| Ū |            |                                                                                                     |            |

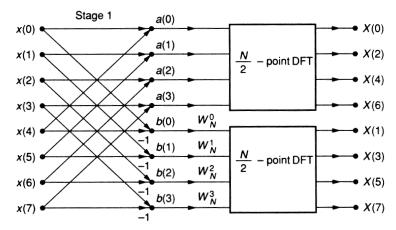

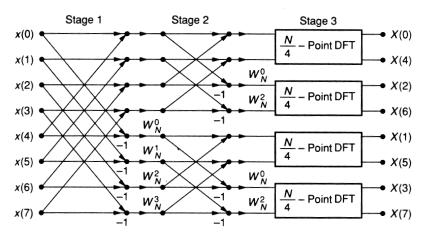

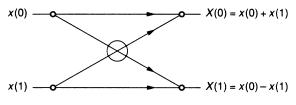

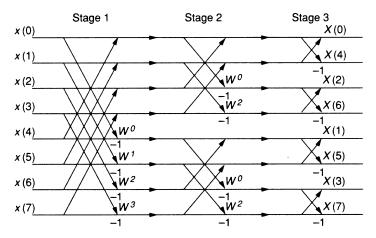

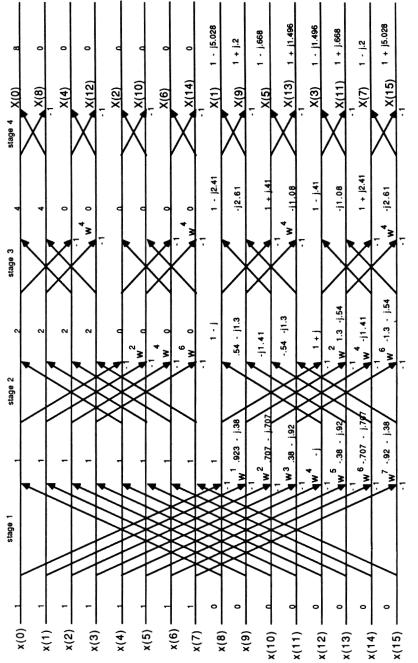

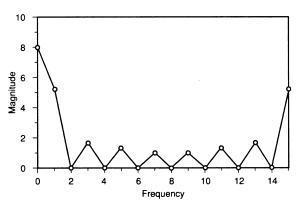

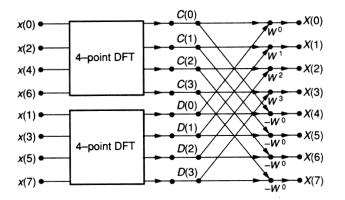

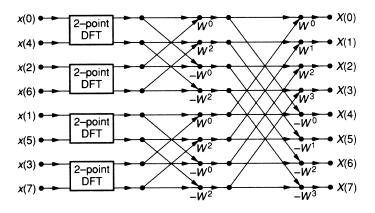

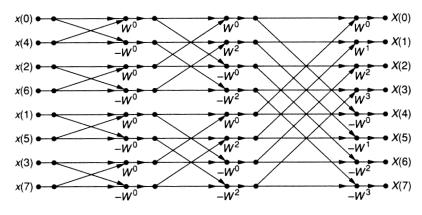

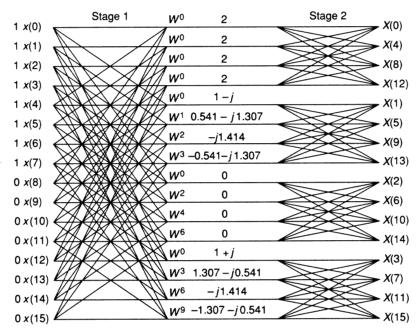

|   | 6.1<br>6.2 | Introduction<br>Development of the FFT Algorithm with Radix-2                                       | 165<br>165 |

|   | 6.2        | Decimation-in-Frequency FFT Algorithm with Radix-2                                                  |            |

|   |            | Decimation-in-Frequency FFT Algorithm with Radix-2<br>Decimation-in-Time FFT Algorithm with Radix-2 | 167        |

|   | 6.4<br>6.5 | Bit Reversal for Unscrambling                                                                       | 174<br>178 |

|   | 6.6        | Development of the FFT Algorithm with Radix-4                                                       | 178        |

|   | 6.7        | Inverse Fast Fourier Transform                                                                      | 1/9        |

|   | 6.8        | Programming Examples Using C and TMS320C3x Code                                                     | 183        |

|   | 0.8<br>6.9 | Experiment 6: FFT Implementation                                                                    | 183        |

|   |            | experiment 0.1111 implementation                                                                    | 193        |

|   | 1.010      |                                                                                                     |            |

#### vi Contents

|    |                                                               | Contents                                 | vii |  |

|----|---------------------------------------------------------------|------------------------------------------|-----|--|

| 7  | ADAPTIVE FILTERS                                              |                                          | 195 |  |

|    | 7.1 Introduction                                              |                                          | 195 |  |

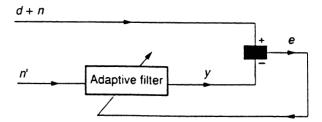

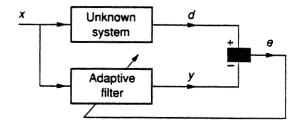

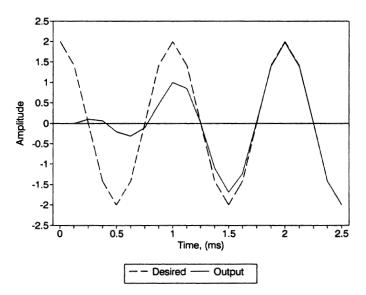

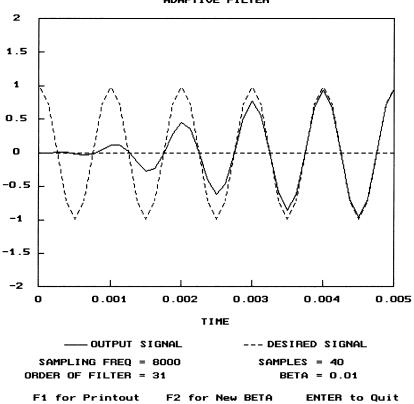

|    | 7.2 Adaptive Structures                                       |                                          | 197 |  |

|    | 7.3 Programming Example                                       | es Using C and TMS320C3x Code            | 199 |  |

|    | 7.4 Experiment 7: Adaptiv                                     | e Filtering Implementation               | 221 |  |

|    | References                                                    |                                          | 222 |  |

| 8  | DSP APPLICATIONS AN                                           | D PROJECTS                               | 223 |  |

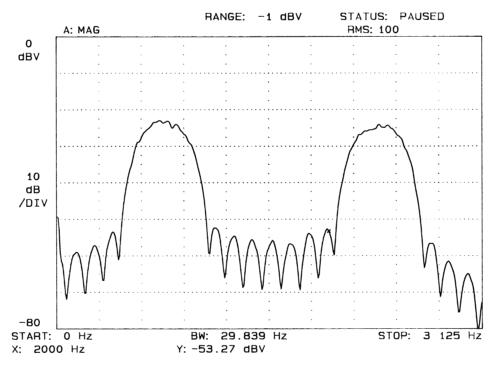

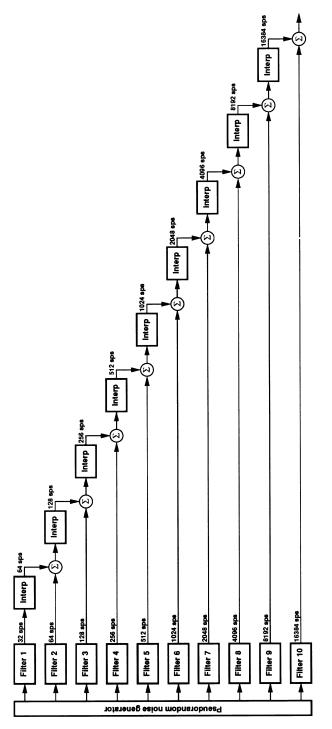

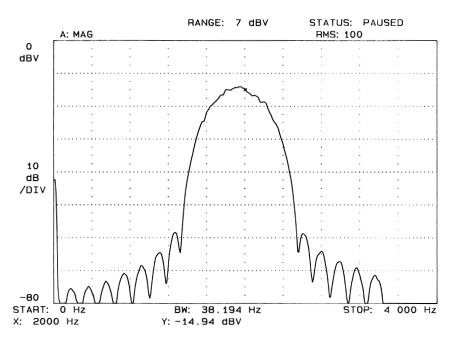

|    | 8.1 Banks of FIR Filters                                      |                                          | 223 |  |

|    | 8.2 Multirate Filter                                          |                                          | 228 |  |

|    | 8.3 Pass/Fail Alarm Gener                                     | rator                                    | 235 |  |

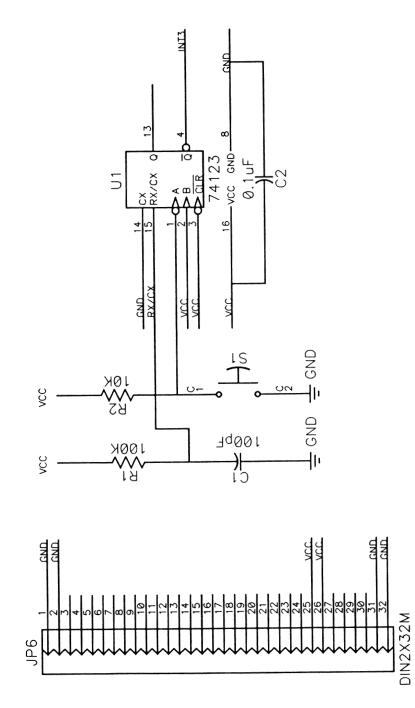

|    | 8.4 External Interrupt for                                    | Control                                  | 239 |  |

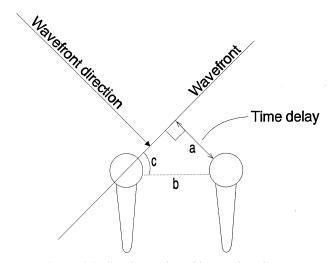

|    | 8.5 Miscellaneous Applica                                     | ations and Projects                      | 242 |  |

|    | References                                                    |                                          | 254 |  |

| AF | PPENDIX A TMS320C3X                                           | 257                                      |     |  |

|    | A.1 TMS320C3x Instructi                                       | ion Set                                  | 257 |  |

|    | A.2 TMS320C3x Register                                        | -s                                       | 257 |  |

|    | Reference                                                     |                                          | 263 |  |

| Ał | PPENDIX B SUPPORT TO                                          | DOLS                                     | 265 |  |

|    | B.1 Code Explorer Debug                                       | ger from GO DSP                          | 265 |  |

|    | B.2 Virtual Instrument Us                                     | ing Shareware Utility Package            | 269 |  |

|    | B.3 Filter Design and Imp                                     | lementation Using DigiFilter             | 271 |  |

|    | B.4 MATLAB for FIR/IIR                                        | Filter Design, FFT, and Data Acquisition | 275 |  |

|    | References                                                    |                                          | 281 |  |

| AF | PPENDIX C EXTERNAL                                            | AND FLASH MEMORY                         | 283 |  |

|    | C.1 External Memory                                           |                                          | 286 |  |

|    | C.2 Flash Memory                                              |                                          | 287 |  |

|    | References                                                    |                                          | 289 |  |

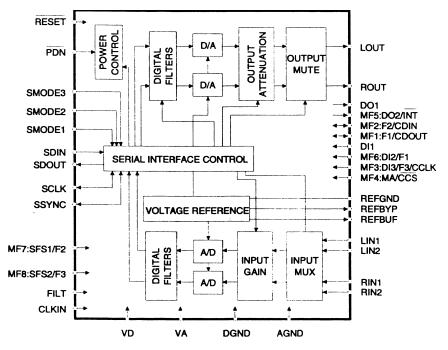

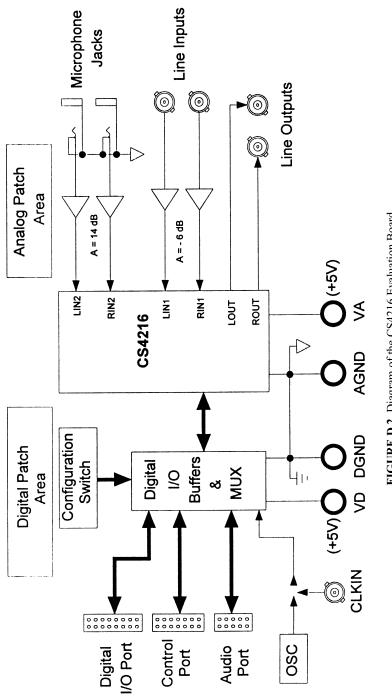

| Ał | APPENDIX D INPUT AND OUTPUT WITH 16-BIT STEREO<br>AUDIO CODEC |                                          |     |  |

|    | References                                                    |                                          | 298 |  |

| In | ıdex                                                          |                                          | 299 |  |

### Preface

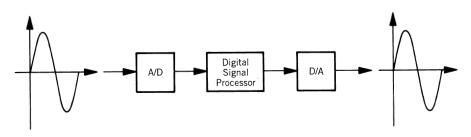

Digital signal processors, such as the TMS320 family of processors, are found in a wide range of applications such as in communications and controls, speech processing, and so on. They are used in Fax, modems, cellular phones, etc. These devices have also found their way into the university classroom, where they provide an economical way to introduce real-time digital signal processing (DSP) to the student.

With the introduction of Texas Instruments' third-generation TMS320C3x processor, floating-point instructions and a new architecture that supports features which facilitate the development of high-level language compilers appeared. The C optimizing compiler takes advantage of the special features of the TMS320C3x processor such as parallel instructions and delayed branches. Throughout the book, we refer to the C/C++ language as simply C. Generally, the price paid for going to a high-level language is a reduction in speed and a similar increase in the size of the executable file. Although TMS320C3x/assembly language produces fast code, problems with documentation and maintenance may exist. A compromise solution is to write time-critical routines in TMS320C3x code that can be called from C.

This book is intended primarily for senior undergraduate and first-year graduate students in electrical and computer engineering and as a tutorial for the practicing engineer. It is written with the conviction that the principles of DSP can best be learned through interaction in a laboratory setting, where the student can appreciate the concepts of DSP through real-time implementation of experiments and projects. The background assumed is a system course and some knowledge of assembly language or a high-level language such as C.

Most chapters begin with a theoretical discussion, followed by representative examples that provide the necessary background to perform the concluding experiments. There are a total of 60 solved programming examples using both TMS320C3x and C code. Several sample projects are also discussed.

Programming examples using both TMS320C3x and C code are included throughout the text. This can be useful to the reader who is familiar with both DSP and C programming, but who is not necessarily an expert in both. Although the

ix

#### X Preface

reader who elects to study the programming examples in either TMS320C3x or C code will benefit from this book, the ideal reader is one with an appreciation for both TMS320C3x and C code.

This book can be used in the following ways:

- For a laboratory course using many of the Examples and Experiments from Chapters 1-7. The beginning of the semester can be devoted to short programming examples and experiments and the remainder of the semester used for a final project.

- For a senior undergraduate or first-year graduate design project course, using Chapters 1-5, selected materials from Chapters 6-8, and Appendices C and D.

- 3. For the practicing engineer as a tutorial and for workshops and seminars.

Chapter 1 introduces the tools through three examples. These tools include an assembler and a debugger that are provided with the DSP Starter Kit (DSK). Program examples in C can be tested without a C compiler since all associated executables files are on the accompanying disk. Chapter 2 covers the architecture and the instructions available for the TMS320C3x processor. Special instructions and assembler directives that are useful in DSP are discussed. Chapter 3 illustrates input and output (I/O) with the two-input analog interface chip (AIC) on the DSK board through several programming examples. An alternative I/O with a 16-bit stereo audio codec that can be interfaced with the DSK is described.

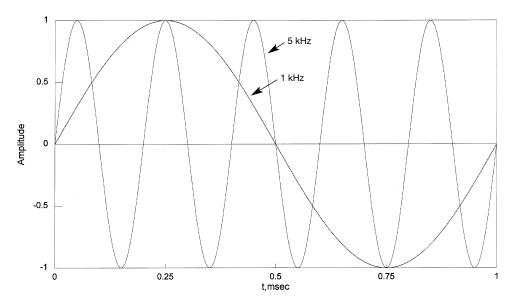

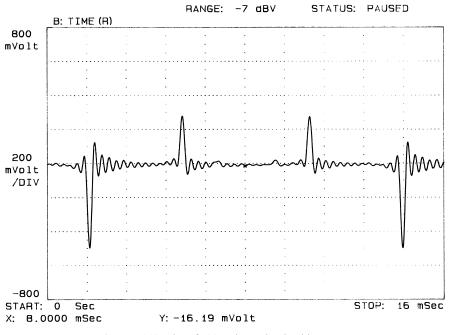

Chapter 4 introduces the z-transform and discusses finite impulse response (FIR) filters and the effect of window functions on these filters. Chapter 5 covers infinite impulse response (IIR) filters. Programming examples to implement FIR and IIR filters, in both TMS320C3x and C code, are included.

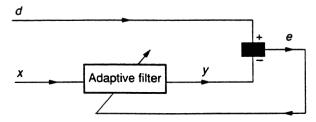

Chapter 6 covers the development of the fast Fourier transform (FFT). Programming examples on FFT are included. Chapter 7 demonstrates the usefulness of the adaptive filter for a number of applications with the least mean square (LMS). Chapter 8 discusses a number of DSP applications.

A disk included with this book contains all the programs discussed in the text. See page xv for a list of the programs/files included on the disk.

During the summers of 1996-1998, a total of 115 faculty members from over 100 Institutions took my DSP and Applications workshops supported by grants from the National Science Foundation (NSF). I am thankful to them for their encouragement, participation and feedback on this book. In particular, Dr. Hisham Alnajjar from the University of Hartford, Dr. Armando Barreto from Florida International University, Dr. Paul Giolma from Trinity University, Dr. William Monaghan from the College of Staten Island—CUNY, and Dr. Mark Wickert from the University of Colorado at Colorado Springs. I also thank Dr. Darrell Horning from the University of New Haven, with whom I coauthored the text *Digital Signal Processing with the TMS320C25*, for introducing me to book-writing. I thank all the students who have taken my DSP and Senior Design Project courses. I am particularly indebted to two former students, Bill Bitler and Peter Martin, who have worked with me for many

years and have contributed to this book as well as to my previous book *Digital Sig*nal Processing with C and the TMS320C30.

The support of the National Science Foundation's Undergraduate Faculty Enhancement (UFE) Program in the Division of Undergraduate Education, Texas Instruments, and the Roger Williams University Research Foundation is appreciated.

RULPH CHASSAING

## **List of Examples**

| 1.1  | Matrix/vector multiplication using TMS320C3x code                   | 4   |

|------|---------------------------------------------------------------------|-----|

|      | Sine generation with 4 points using TMS320C3x code                  | 8   |

| 1.3  | Matrix/vector multiplication using C code                           | 11  |

| 2.1  | Addition of four values using TMS320C3x code                        | 34  |

| 2.2  | Multiplication of two arrays using TMS320C3x code                   | 35  |

| 2.3  | Background for digital filtering using TMS320C3x code               | 37  |

| 2.4  | Matrix/vector multiplication using TMS320C3x code                   | 42  |

| 2.5  | Addition using C and C-called TMS320C3x assembly function           | 42  |

| 2.6  | Matrix/vector multiplication using C and C-called TMS320C3x         | 45  |

|      | assembly function                                                   |     |

| 3.1  | Internal interrupt using TMS320C3x code                             | 60  |

| 3.2  | Sine generation with AIC data using TMS320C3x code                  | 62  |

| 3.3  | Loop/echo with AIC routines in separate file, using TMS320C3x code  | 65  |

| 3.4  | Loop/echo with interrupt using TMS320C3x code                       | 69  |

| 3.5  | Sine generation with interrupt using TMS320C3x code                 | 70  |

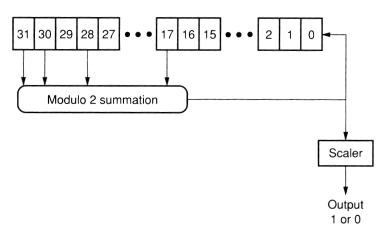

| 3.6  | Pseudorandom noise generation using TMS320C3x code                  | 70  |

| 3.7  | Alternative pseudorandom noise generation with interrupt using      | 73  |

|      | TMS320C3x code                                                      |     |

| 3.8  | Loop/echo with AIC data using C code                                | 75  |

| 3.9  | Loop/echo Calling AIC routines in separate file, using C code       | 75  |

| 3.10 | D Loop/echo with interrupt using C code                             | 79  |

| 3.1  | 1 PC-TMS320C31 communication using C code                           | 82  |

| 3.12 | 2 Loop control with PC-TMS320C31 communication using C code         | 84  |

| 3.13 | 3 Data acquisition with the DSK using C and TMS320C3x code          | 85  |

| 4.1  | FIR lowpass filter simulation with 11 coefficients using TMS320C3x  | 108 |

|      | code                                                                |     |

| 4.2  | FIR bandpass filter simulation with 45 coefficients using TMS320C3x | 111 |

|      | code                                                                |     |

| 4.3  | Generic FIR filter specified at run-time, using TMS320C3x code      | 112 |

| 4.4  | FIR filter incorporating pseudorandom noise as input, using         | 115 |

|      | TMS320C3x code                                                      |     |

xiii

| 4.7FIR filter using C code1234.8FIR filter with samples shifted, using C code1254.9FIR filter design using filter development package1275.1Sine generation by recursive equation using TMS320C3x code1525.2Cosine generation by recursive equation using C code1545.3Sine generation by recursive equation using C code1545.4Sixth-order IIR bandpass filter using TMS320C3x code1565.5Sixth-order IIR bandpass filter using C code1606.1Eight-point FFT with real-valued Input, using mixed C and<br>TMS320C3x code1876.2Eight-point FFT using mixed code1917.1Adaptive filter for noise cancellation using C code2037.3Adaptive predictor using C code2067.4Adaptive predictor using C code2067.5Adaptive predictor using C code2067.6Adaptive predictor using TMS320C3x code2167.7Real-time adaptive filter for noise cancellation using TMS320C3x code2167.8Adaptive predictor using TMS320C3x code2167.9Real-time adaptive filter for noise cancellation, using TMS320C3x code2167.4Real-time adaptive filter for noise cancellation, using TMS320C3x code2167.9FIR filter design and implementation using DigiFilter2727.9IIR filter design and implementation using DigiFilter2748.4FIR filter design using MATLAB2758.5Multibahd FIR filter design using MATLAB                                                        | 4.5         | Mixed-code FIR filter with main C program calling filter function in TMS320C3x code | 117 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------|-----|

| 4.8FIR filter with samples shifted, using C code1254.9FIR filter design using filter development package1275.1Sine generation by recursive equation using TMS320C3x code1525.2Cosine generation by recursive equation using C code1545.3Sine generation by recursive equation using C code1545.4Sixth-order IIR bandpass filter using C code1666.5Sixth-order IIR bandpass filter using C code1666.1Eight-point complex FFT using C code1846.2Eight-point FFT with real-valued Input, using mixed C and<br>TMS320C3x code1877.1Adaptive filter using C code compiled with Borland C/C++2007.2Adaptive filter for noise cancellation using C code2067.3Adaptive predictor using C code2067.4Adaptive predictor using C code2067.5Adaptive predictor using C code2067.6Adaptive predictor using TMS320C3x code2157.7Real-time adaptive filter for noise cancellation, using TMS320C3x code2168.1FIR filter using Code Explorer for debugging and plotting2658.2FIR filter design and implementation using DigiFilter2728.3IIR filter design using MATLAB2768.4FIR filter design using MATLAB2768.5Multiband FIR filter diseng using MATLAB2768.6Eight-point FFT and IFFT using MATLAB2768.7H(z) from H(s) using bilinear function in MATLAB2768.8 </td <td>4.6</td> <td>FIR filter with data move using C code</td> <td>121</td> | 4.6         | FIR filter with data move using C code                                              | 121 |

| 4.9FIR filter design using filter development package1275.1Sine generation by recursive equation using TMS320C3x code1525.2Cosine generation by recursive equation using TMS320C3x code1545.3Sine generation by recursive equation using C code1545.4Sixth-order IIR bandpass filter using TMS320C3x code1565.5Sixth-order IIR bandpass filter using C code1606.1Eight-point complex FFT using C code1846.2Eight-point FFT with real-valued Input, using mixed C and<br>TMS320C3x code1877.1Adaptive filter using C code compiled with Borland C/C++2007.2Adaptive filter for noise cancellation using C code2037.3Adaptive predictor using C code2067.4Adaptive predictor using C code2067.5Adaptive predictor using TMS320C3x code2167.6Adaptive predictor using TMS320C3x code2167.7Real-time adaptive filter for noise cancellation, using TMS320C3x code2167.8Adaptive predictor using TMS320C3x code2167.7Real-time adaptive filter for noise cancellation, using TMS320C3x code2167.8Real-time adaptive filter for noise cancellation, using TMS320C3x code2168.1FIR filter design and implementation using DigiFilter2728.3IIR filter design and implementation using DigiFilter2748.4FIR filter design using MATLAB2768.5Multiband FIR filter design using MATLAB2768.6                                               | 4.7         | FIR filter using C code                                                             | 123 |

| 5.1Sine generation by recursive equation using TMS320C3x code1525.2Cosine generation by recursive equation using TMS320C3x code1545.3Sine generation by recursive equation using C code1545.4Sixth-order IIR bandpass filter using TMS320C3x code1565.5Sixth-order IIR bandpass filter using C code1606.1Eight-point complex FFT using C code1846.2Eight-point FFT with real-valued Input, using mixed C and<br>TMS320C3x code1877.1Adaptive filter using C code compiled with Borland C/C++2007.2Adaptive filter for noise cancellation using C code2087.3Adaptive predictor using C code2087.4Adaptive predictor with table lookup for delay, using C code2087.5Adaptive predictor using TMS320C3x code2157.6Adaptive predictor using TMS320C3x code2167.7Real-time adaptive filter for noise cancellation, using TMS320C3x code2188.1FIR filter design and implementation using DigiFilter2728.2FIR filter design and implementation using DigiFilter2748.4FIR filter design using MATLAB2768.5Multiband FIR filter design using MATLAB2768.6IIR filter design using MATLAB2768.7H(z) from H(s) using bilinear function in MATLAB2768.8Eight-point FFT and IFFT using MATLAB2768.9Data acquisition, plotting, and FFT using MATLAB2768.9Data acquisition, plotting, and F                                                   | 4.8         | FIR filter with samples shifted, using C code                                       | 125 |

| 5.2Cosine generation by recursive equation using TMS320C3x code1545.3Sine generation by recursive equation using C code1545.4Sixth-order IIR bandpass filter using TMS320C3x code1665.5Sixth-order IIR bandpass filter using C code1846.1Eight-point complex FFT using C code1846.2Eight-point FFT with real-valued Input, using mixed C and<br>TMS320C3x code1877.1Adaptive filter using C code compiled with Borland C/C++2007.2Adaptive filter for noise cancellation using C code2037.3Adaptive predictor using C code2067.4Adaptive predictor with table lookup for delay, using C code2067.5Adaptive predictor using TMS320C3x code2157.6Adaptive predictor using TMS320C3x code2167.7Real-time adaptive filter for noise cancellation, using TMS320C3x code2188.1FIR filter design and implementation using DigiFilter2728.2FIR filter design and implementation using DigiFilter2748.4FIR filter design using MATLAB2768.5Multiband FIR filter design using MATLAB2768.6IIR filter design using MATLAB2768.7H(z) from H(s) using bilinear function in MATLAB2768.8Eight-point FFT and IFFT using MATLAB2768.9Data acquisition, plotting, and FFT using MATLAB2768.7Multirate filter with 10 bands using external memory and287                                                                                         | 4.9         | FIR filter design using filter development package                                  | 127 |

| 5.3Sine generation by recursive equation using C code1545.4Sixth-order IIR bandpass filter using TMS320C3x code1565.5Sixth-order IIR bandpass filter using C code1606.1Eight-point complex FFT using C code1846.2Eight-point FFT with real-valued Input, using mixed C and<br>TMS320C3x code1877.1Adaptive filter using C code compiled with Borland C/C++2007.2Adaptive filter for noise cancellation using C code2037.3Adaptive predictor using C code2067.4Adaptive predictor using C code2067.5Adaptive predictor with table lookup for delay, using C code2067.6Adaptive predictor using TMS320C3x code2157.7Real-time adaptive filter for noise cancellation, using TMS320C3x code2167.6Adaptive predictor using TMS320C3x code2188.1FIR filter using Code Explorer for debugging and plotting2658.2FIR filter design and implementation using DigiFilter2768.3IIR filter design using MATLAB2768.4FIR filter design using MATLAB2768.5Multiband FIR filter design using MATLAB2768.6IIR filter design using MATLAB2768.7H(z) from H(s) using bilinear function in MATLAB2768.8Eight-point FFT and IFFT using MATLAB2768.9Data acquisition, plotting, and FFT using MATLAB2768.9Data acquisition, plotting, and FFT using MATLAB2768.9                                                                                   |             |                                                                                     | 152 |

| 5.4Sixth-order IIR bandpass filter using TMS320C3x code1565.5Sixth-order IIR bandpass filter using C code1606.1Eight-point complex FFT using C code1846.2Eight-point FFT with real-valued Input, using mixed C and<br>TMS320C3x code1876.3Real-time 128-Point FFT using mixed code1917.1Adaptive filter using C code compiled with Borland C/C++2007.2Adaptive filter for noise cancellation using C code2037.3Adaptive predictor using C code2067.4Adaptive predictor using C code2067.5Adaptive predictor using TMS320C3x code2157.6Adaptive predictor using TMS320C3x code2157.7Real-time adaptive filter for noise cancellation, using TMS320C3x code2188.1FIR filter using Code Explorer for debugging and plotting2658.2FIR filter design and implementation using DigiFilter2728.3IIR filter design and implementation using DigiFilter2748.4FIR filter design using MATLAB2768.5Multiband FIR filter design using MATLAB2768.6IIR filter design using MATLAB2768.7H(z) from H(s) using bilinear function in MATLAB2758.9Data acquisition, plotting, and FFT using MATLAB2758.9Data acquisition, plotting, and FFT using MATLAB2758.9Data acquisition, plotting, and FFT using MATLAB2758.7Multirate filter with 10 bands using external memory and287<                                                                 | 5.2         | Cosine generation by recursive equation using TMS320C3x code                        | 154 |

| 5.5Sixth-order IIR bandpass filter using C code1606.1Eight-point complex FFT using C code1846.2Eight-point FFT with real-valued Input, using mixed C and<br>TMS320C3x code1876.3Real-time 128-Point FFT using mixed code1917.1Adaptive filter using C code compiled with Borland C/C++2007.2Adaptive filter for noise cancellation using C code2037.3Adaptive predictor using C code2067.4Adaptive predictor using C code2067.5Adaptive predictor with table lookup for delay, using C code2087.6Adaptive predictor using TMS320C3x code2157.7Real-time adaptive filter for noise cancellation, using TMS320C3x code2168.1FIR filter design and implementation using DigiFilter2728.2FIR filter design and implementation using DigiFilter2748.4FIR filter design using MATLAB2758.5Multiband FIR filter design using MATLAB2768.6IIR filter design using MATLAB2768.7H(z) from H(s) using bilinear function in MATLAB2788.8Eight-point FFT and IFFT using MATLAB2798.9Data acquisition, plotting, and FFT using MATLAB2798.9Data acquisition, plotting, and FFT using MATLAB279C.1Multirate filter with 10 bands using external memory and287                                                                                                                                                                                 | 5.3         | Sine generation by recursive equation using C code                                  | 154 |

| 6.1 Eight-point complex FFT using C code1846.2 Eight-point FFT with real-valued Input, using mixed C and<br>TMS320C3x code1876.3 Real-time 128-Point FFT using mixed code1917.1 Adaptive filter using C code compiled with Borland C/C++2007.2 Adaptive filter for noise cancellation using C code2037.3 Adaptive predictor using C code2067.4 Adaptive predictor with table lookup for delay, using C code2067.5 Adaptive predictor with table lookup for delay, using C code2087.6 Adaptive predictor using TMS320C3x code2157.7 Real-time adaptive filter for noise cancellation, using TMS320C3x code2188.1 FIR filter design and implementation using DigiFilter2728.3 IIR filter design and implementation using DigiFilter2748.4 FIR filter design using MATLAB2758.5 Multiband FIR filter design using MATLAB2768.6 IIR filter design using MATLAB2768.7 H(z) from H(s) using bilinear function in MATLAB2788.8 Eight-point FFT and IFFT using MATLAB2798.9 Data acquisition, plotting, and FFT using MATLAB279C.1 Multirate filter with 10 bands using external memory and287                                                                                                                                                                                                                                         | 5.4         | Sixth-order IIR bandpass filter using TMS320C3x code                                | 156 |

| 6.2 Eight-point FFT with real-valued Input, using mixed C and<br>TMS320C3x code1876.3 Real-time 128-Point FFT using mixed code1917.1 Adaptive filter using C code compiled with Borland C/C++2007.2 Adaptive filter for noise cancellation using C code2037.3 Adaptive predictor using C code2067.4 Adaptive predictor with table lookup for delay, using C code2067.5 Adaptive predictor with table lookup for delay, using C code2087.6 Adaptive predictor using TMS320C3x code2157.7 Real-time adaptive filter for noise cancellation, using TMS320C3x code2188.1 FIR filter using Code Explorer for debugging and plotting2658.2 FIR filter design and implementation using DigiFilter2728.3 IIR filter design and implementation using DigiFilter2748.4 FIR filter design using MATLAB2758.5 Multiband FIR filter design using MATLAB2768.6 IIR filter design using MATLAB2768.7 H(z) from H(s) using bilinear function in MATLAB2788.8 Eight-point FFT and IFFT using MATLAB2798.9 Data acquisition, plotting, and FFT using MATLAB279C.1 Multirate filter with 10 bands using external memory and287                                                                                                                                                                                                                    | 5.5         | Sixth-order IIR bandpass filter using C code                                        | 160 |

| TMS320C3x code1916.3 Real-time 128-Point FFT using mixed code1917.1 Adaptive filter using C code compiled with Borland C/C++2007.2 Adaptive filter for noise cancellation using C code2037.3 Adaptive predictor using C code2067.4 Adaptive predictor with table lookup for delay, using C code2067.5 Adaptive predictor using TMS320C3x code2167.6 Adaptive predictor using TMS320C3x code2157.7 Real-time adaptive filter for noise cancellation, using TMS320C3x code2188.1 FIR filter using Code Explorer for debugging and plotting2658.2 FIR filter design and implementation using DigiFilter2728.3 IIR filter design and implementation using DigiFilter2748.4 FIR filter design using MATLAB2768.5 Multiband FIR filter design using MATLAB2768.6 IIR filter design using MATLAB2768.7 H(z) from H(s) using bilinear function in MATLAB2788.8 Eight-point FFT and IFFT using MATLAB2798.9 Data acquisition, plotting, and FFT using MATLAB279C.1 Multirate filter with 10 bands using external memory and287                                                                                                                                                                                                                                                                                                          | 6.1         | Eight-point complex FFT using C code                                                | 184 |

| 6.3 Real-time 128-Point FFT using mixed code1917.1 Adaptive filter using C code compiled with Borland C/C++2007.2 Adaptive filter for noise cancellation using C code2037.3 Adaptive predictor using C code2067.4 Adaptive predictor with table lookup for delay, using C code2087.5 Adaptive predictor using TMS320C3x code2167.6 Adaptive predictor using TMS320C3x code2157.7 Real-time adaptive filter for noise cancellation, using TMS320C3x code2188.1 FIR filter using Code Explorer for debugging and plotting2658.2 FIR filter design and implementation using DigiFilter2728.3 IIR filter design and implementation using DigiFilter2748.4 FIR filter design using MATLAB2768.5 Multiband FIR filter design using MATLAB2768.6 IIR filter design using MATLAB2768.7 H(z) from H(s) using bilinear function in MATLAB2788.8 Eight-point FFT and IFFT using MATLAB2798.9 Data acquisition, plotting, and FFT using MATLAB279C.1 Multirate filter with 10 bands using external memory and287                                                                                                                                                                                                                                                                                                                           | 6.2         | Eight-point FFT with real-valued Input, using mixed C and                           | 187 |

| 7.1Adaptive filter using C code compiled with Borland C/C++2007.2Adaptive filter for noise cancellation using C code2037.3Adaptive predictor using C code2067.4Adaptive predictor with table lookup for delay, using C code2067.5Adaptive predictor with table lookup for delay, using C code2067.6Adaptive predictor using TMS320C3x code2167.7Real-time adaptive filter for noise cancellation, using TMS320C3x code2188.1FIR filter using Code Explorer for debugging and plotting2658.2FIR filter design and implementation using DigiFilter2728.3IIR filter design and implementation using DigiFilter2748.4FIR filter design using MATLAB2758.5Multiband FIR filter design using MATLAB2768.6IIR filter design using MATLAB2768.7H(z) from H(s) using bilinear function in MATLAB2788.8Eight-point FFT and IFFT using MATLAB2798.9Data acquisition, plotting, and FFT using MATLAB279C.1Multirate filter with 10 bands using external memory and287                                                                                                                                                                                                                                                                                                                                                                      |             | TMS320C3x code                                                                      |     |

| 7.2Adaptive filter for noise cancellation using C code2037.3Adaptive predictor using C code2067.4Adaptive predictor with table lookup for delay, using C code2067.5Adaptive predictor with table lookup for delay, using C code2067.5Adaptive predictor using TMS320C3x code2167.6Adaptive predictor using TMS320C3x code2157.7Real-time adaptive filter for noise cancellation, using TMS320C3x code2188.1FIR filter using Code Explorer for debugging and plotting2658.2FIR filter design and implementation using DigiFilter2728.3IIR filter design and implementation using DigiFilter2748.4FIR filter design using MATLAB2758.5Multiband FIR filter design using MATLAB2768.6IIR filter design using MATLAB2768.7H(z) from H(s) using bilinear function in MATLAB2788.8Eight-point FFT and IFFT using MATLAB2798.9Data acquisition, plotting, and FFT using MATLAB279C.1Multirate filter with 10 bands using external memory and287                                                                                                                                                                                                                                                                                                                                                                                       | 6.3         | Real-time 128-Point FFT using mixed code                                            | 191 |

| 7.3Adaptive predictor using C code2067.4Adaptive predictor with table lookup for delay, using C code2087.5Adaptive notch filter with two weights, using TMS320C3x code2107.6Adaptive predictor using TMS320C3x code2157.7Real-time adaptive filter for noise cancellation, using TMS320C3x code2188.1FIR filter using Code Explorer for debugging and plotting2658.2FIR filter design and implementation using DigiFilter2728.3IIR filter design and implementation using DigiFilter2748.4FIR filter design using MATLAB2758.5Multiband FIR filter design using MATLAB2768.6IIR filter design using MATLAB2768.7H(z) from H(s) using bilinear function in MATLAB2788.8Eight-point FFT and IFFT using MATLAB2798.9Data acquisition, plotting, and FFT using MATLAB279C.1Multirate filter with 10 bands using external memory and287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7.1         | Adaptive filter using C code compiled with Borland C/C++                            | 200 |

| 7.4Adaptive predictor with table lookup for delay, using C code2087.5Adaptive notch filter with two weights, using TMS320C3x code2107.6Adaptive predictor using TMS320C3x code2157.7Real-time adaptive filter for noise cancellation, using TMS320C3x code218B.1FIR filter using Code Explorer for debugging and plotting265B.2FIR filter design and implementation using DigiFilter272B.3IIR filter design and implementation using DigiFilter274B.4FIR filter design using MATLAB275B.5Multiband FIR filter design using MATLAB276B.6IIR filter design using MATLAB276B.7H(z) from H(s) using bilinear function in MATLAB278B.8Eight-point FFT and IFFT using MATLAB279C.1Multirate filter with 10 bands using external memory and287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7.2         | Adaptive filter for noise cancellation using C code                                 | 203 |

| 7.5 Adaptive notch filter with two weights, using TMS320C3x code2107.6 Adaptive predictor using TMS320C3x code2157.7 Real-time adaptive filter for noise cancellation, using TMS320C3x code2188.1 FIR filter using Code Explorer for debugging and plotting2658.2 FIR filter design and implementation using DigiFilter2728.3 IIR filter design and implementation using DigiFilter2748.4 FIR filter design using MATLAB2758.5 Multiband FIR filter design using MATLAB2768.6 IIR filter design using MATLAB2768.7 H(z) from H(s) using bilinear function in MATLAB2788.8 Eight-point FFT and IFFT using MATLAB2798.9 Data acquisition, plotting, and FFT using MATLAB279C.1 Multirate filter with 10 bands using external memory and287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7.3         | Adaptive predictor using C code                                                     | 206 |

| 7.6Adaptive predictor using TMS320C3x code2157.7Real-time adaptive filter for noise cancellation, using TMS320C3x code2188.1FIR filter using Code Explorer for debugging and plotting2658.2FIR filter design and implementation using DigiFilter2728.3IIR filter design and implementation using DigiFilter2748.4FIR filter design using MATLAB2758.5Multiband FIR filter design using MATLAB2768.6IIR filter design using MATLAB2768.7H(z) from H(s) using bilinear function in MATLAB2788.8Eight-point FFT and IFFT using MATLAB2798.9Data acquisition, plotting, and FFT using MATLAB279C.1Multirate filter with 10 bands using external memory and287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7.4         | Adaptive predictor with table lookup for delay, using C code                        | 208 |

| 7.7 Real-time adaptive filter for noise cancellation, using TMS320C3x code218B.1 FIR filter using Code Explorer for debugging and plotting265B.2 FIR filter design and implementation using DigiFilter272B.3 IIR filter design and implementation using DigiFilter274B.4 FIR filter design using MATLAB275B.5 Multiband FIR filter design using MATLAB276B.6 IIR filter design using MATLAB276B.7 H(z) from H(s) using bilinear function in MATLAB278B.8 Eight-point FFT and IFFT using MATLAB279B.9 Data acquisition, plotting, and FFT using MATLAB279C.1 Multirate filter with 10 bands using external memory and287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7.5         | Adaptive notch filter with two weights, using TMS320C3x code                        | 210 |

| B.1 FIR filter using Code Explorer for debugging and plotting265B.2 FIR filter design and implementation using DigiFilter272B.3 IIR filter design and implementation using DigiFilter274B.4 FIR filter design using MATLAB275B.5 Multiband FIR filter design using MATLAB276B.6 IIR filter design using MATLAB277B.7 H(z) from H(s) using bilinear function in MATLAB278B.8 Eight-point FFT and IFFT using MATLAB279B.9 Data acquisition, plotting, and FFT using MATLAB279C.1 Multirate filter with 10 bands using external memory and287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7.6         | Adaptive predictor using TMS320C3x code                                             | 215 |

| B.2FIR filter design and implementation using DigiFilter272B.3IIR filter design and implementation using DigiFilter274B.4FIR filter design using MATLAB275B.5Multiband FIR filter design using MATLAB276B.6IIR filter design using MATLAB276B.7H(z) from H(s) using bilinear function in MATLAB278B.8Eight-point FFT and IFFT using MATLAB279B.9Data acquisition, plotting, and FFT using MATLAB279C.1Multirate filter with 10 bands using external memory and287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7.7         | Real-time adaptive filter for noise cancellation, using TMS320C3x code              | 218 |

| B.3 IIR filter design and implementation using DigiFilter274B.4 FIR filter design using MATLAB275B.5 Multiband FIR filter design using MATLAB276B.6 IIR filter design using MATLAB277B.7 H(z) from H(s) using bilinear function in MATLAB278B.8 Eight-point FFT and IFFT using MATLAB279B.9 Data acquisition, plotting, and FFT using MATLAB279C.1 Multirate filter with 10 bands using external memory and287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | B.1         | FIR filter using Code Explorer for debugging and plotting                           | 265 |

| B.4 FIR filter design using MATLAB275B.5 Multiband FIR filter design using MATLAB276B.6 IIR filter design using MATLAB277B.7 H(z) from H(s) using bilinear function in MATLAB278B.8 Eight-point FFT and IFFT using MATLAB279B.9 Data acquisition, plotting, and FFT using MATLAB279C.1 Multirate filter with 10 bands using external memory and287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | B.2         | FIR filter design and implementation using DigiFilter                               | 272 |

| B.5Multiband FIR filter design using MATLAB276B.6IIR filter design using MATLAB277B.7H(z) from H(s) using bilinear function in MATLAB278B.8Eight-point FFT and IFFT using MATLAB279B.9Data acquisition, plotting, and FFT using MATLAB279C.1Multirate filter with 10 bands using external memory and287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | B.3         | IIR filter design and implementation using DigiFilter                               | 274 |

| B.6 IIR filter design using MATLAB277B.7 H(z) from H(s) using bilinear function in MATLAB278B.8 Eight-point FFT and IFFT using MATLAB279B.9 Data acquisition, plotting, and FFT using MATLAB279C.1 Multirate filter with 10 bands using external memory and287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | B.4         | FIR filter design using MATLAB                                                      | 275 |

| B.7 H(z) from H(s) using bilinear function in MATLAB278B.8 Eight-point FFT and IFFT using MATLAB279B.9 Data acquisition, plotting, and FFT using MATLAB279C.1 Multirate filter with 10 bands using external memory and287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | B.5         | Multiband FIR filter design using MATLAB                                            | 276 |

| B.8 Eight-point FFT and IFFT using MATLAB279B.9 Data acquisition, plotting, and FFT using MATLAB279C.1 Multirate filter with 10 bands using external memory and287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | B.6         | IIR filter design using MATLAB                                                      | 277 |

| B.9 Data acquisition, plotting, and FFT using MATLAB279C.1 Multirate filter with 10 bands using external memory and287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>B.</b> 7 | H(z) from H(s) using bilinear function in MATLAB                                    | 278 |

| C.1 Multirate filter with 10 bands using external memory and 287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>B.</b> 8 | Eight-point FFT and IFFT using MATLAB                                               | 279 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B.9         | Data acquisition, plotting, and FFT using MATLAB                                    | 279 |

| TMS320C3x code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | C.1         | Multirate filter with 10 bands using external memory and                            | 287 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | TMS320C3x code                                                                      |     |

| C.2 Sine generation with four points from flash memory, using C code 287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | C.2         | Sine generation with four points from flash memory, using C code                    | 287 |

| C.3 FIR bandpass filter from flash memory using C code 289                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | C.3         | FIR bandpass filter from flash memory using C code                                  | 289 |

| D.1 Loop programs for input and output with the Crystal 16-bit stereo 297 audio codec using TMS320C3x code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D.1         |                                                                                     | 297 |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D.2         | •                                                                                   | 298 |

## List of Programs/Files on Accompanying Disk

| README          | TXT   | 169  | Directory of CH | 3   |        |

|-----------------|-------|------|-----------------|-----|--------|

| EGAVGA          | BGI   | 5363 | INTERR          | ASM | 1915   |

|                 |       |      | SINEALL         | ASM | 3093   |

| Directory of CH | []    |      | LOOP            | ASM | 838    |

| MATRIX          | ASM   | 1628 | LOOPI           | ASM | 1076   |

| SINE4P          | ASM   | 1118 | SINE8I          | ASM | 1539   |

| MATRIXC         | ASM   | 6860 | PRNOISE         | ASM | 1829   |

| MATRIXC         | C     | 482  | PRNOISEI        | ASM | 2214   |

| MATRIXC         | CMD   | 750  | VECS_DSK        | ASM | 222    |

| MATRIXC         | OUT   | 1901 | LOOPALL         | ASM | 8525   |

| AICCOM31        | ASM   | 5308 | LOOPC           | ASM | 9635   |

| AICCOMST        | ASIVI | 5500 | PCLOOP          | EXE | 212306 |

| Directory of CH | 12    |      | C31COM          | ASM | 3169   |

|                 |       |      | DAQ             | EXE | 250093 |

| ADD4            | ASM   | 702  | DAQ             | ASM | 9627   |

| MULT4           | ASM   | 1150 | LOOPALL         | С   | 2488   |

| FIR4            | ASM   | 3016 | AICCOMC         | С   | 2271   |

| MATRIXMF        | ASM   | 1369 | LOOPC           | С   | 610    |

| ADDMFUNC        | ASM   | 556  | LOOPCI          | С   | 740    |

| ADDM            | ASM   | 4179 | C31COM          | С   | 439    |

| FIR11           | ASM   | 2595 | C31LOOP         | С   | 873    |

| ADDM            | С     | 393  | LOOPALL         | CMD | 991    |

| MATRIXM         | С     | 488  | LOOPCI          | CMD | 1029   |

| ADDM            | CMD   | 804  | C31COM          | CMD | 905    |

| ADDM            | OUT   | 1878 | C31LOOP         | CMD | 905    |

| MATRIXM         | OUT   | 2053 | LOOPALL         | OUT | 2100   |

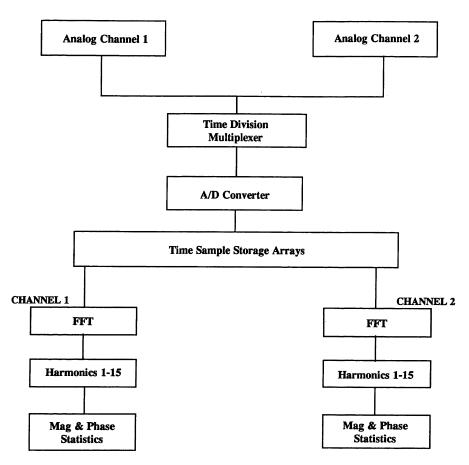

| FIR11L          | DAT   | 190  | LOOPC           | OUT | 2146   |

| FIR11X          | DAT   | 242  | LOOPCI          | OUT | 2422   |

|                 |       |      |                 |     |        |

xv

#### XVI List of Programs/Files on Accompanying Disk

| C31LOOP         | OUT    | 2856   | BP45            | COF   | 843   |

|-----------------|--------|--------|-----------------|-------|-------|

| C31COM          | OUT    | 1664   | BP33            | COF   | 706   |

| PCCOM           | CPP    | 1309   | COMB14          | COF   | 273   |

| PCLOOP          | CPP    | 1033   | KBP53           | COF   | 2426  |

| DAQ             | CPP    | 1632   | RBP53           | COF   | 2424  |

| DAQ             | DAT    | 3117   | BP45COEF        | Н     | 721   |

| DSKLIB          | LIB    | 143872 |                 |       |       |

| SYMBOLS         | Н      | 4190   | Directory of CH | 45    |       |

| DSKLIB          | Н      | 293    |                 |       |       |

| VECS DSK        | OBJ    | 427    | SINEA           | ASM   | 1767  |

| SINEFM          | ASM    | 2622   | COSINEA         | ASM   | 1833  |

| SINCEINI        | 110101 | 2022   | IIR6BP          | ASM   | 2335  |

| Directory of CH | 1/     |        | SINEC           | С     | 1971  |

| Directory of CI | 17     |        | IIR6BPC         | С     | 1057  |

| BP45SIM         | ASM    | 2383   | IIR6BPC         | CMD   | 1033  |

| LP11SIM         | ASM    | 2385   | SINEC           | OUT   | 3986  |

| FIRNC           | ASM    | 2147   | IIR6BPC         | OUT   | 3115  |

| FIRPRN          | ASM    | 3550   | AMPLIT          | CPP   | 17889 |

| FIRMCF          | ASM    | 2016   | BLT             | BAS   | 5363  |

| FIRMC           | ASM    | 16714  | IIR6COEF        | Н     | 639   |

| AICCOMC         | С      | 2233   | SINECMOD        | С     | 2456  |

| FIRDMOVE        | С      | 1106   | SINESW          | ASM   | 2553  |

| FIRERIC         | С      | 1509   |                 |       |       |

| FIRMC           | С      | 713    | Directory of CH | 46    |       |

| FIRC            | Ċ      | 1376   |                 |       |       |

| FIRMC           | CMD    | 1091   | TWID128         | ASM   | 2096  |

| FIRDMOVE        | OUT    | 3018   | FFT_RL          | OBJ   | 1011  |

| FIRERIC         | OUT    | 3113   | FFT_RL          | ASM   | 6358  |

| FIRMC           | OUT    | 3040   | TWID8           | ASM   | 221   |

| FIRC            | OUT    | 3089   | FFT128C         | С     | 2498  |

| BP45SIM         | DAT    | 371    | FFT             | С     | 2294  |

| LP11SIM         | DAT    | 190    | SINEGEN         | С     | 540   |

| FIR             | BAT    | 97     | TWIDGEN         | С     | 814   |

| FIRPROGA        | BAS    | 20237  | FFT8C           | С     | 680   |

|                 |        |        | FFT8MC          | С     | 1124  |

| FIRPROG         | BAS    | 17752  | FFT128C         | CMD   | 1033  |

| BP55            | COF    | 1080   | FFT128C         | OUT   | 8327  |

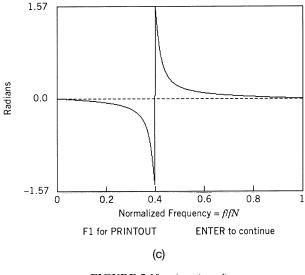

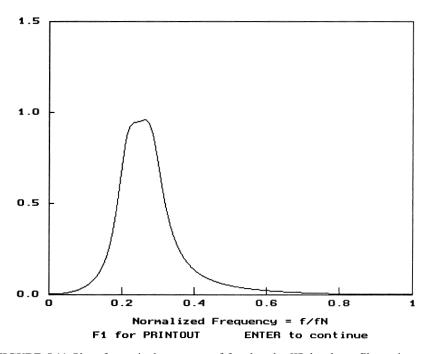

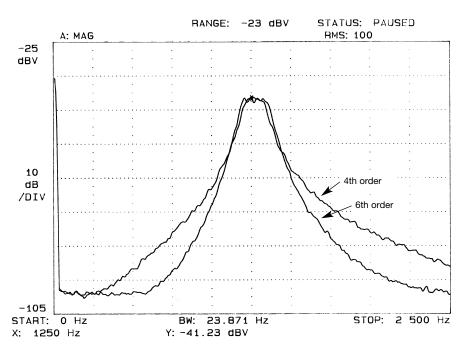

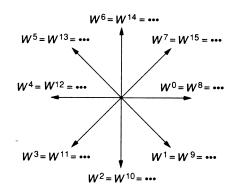

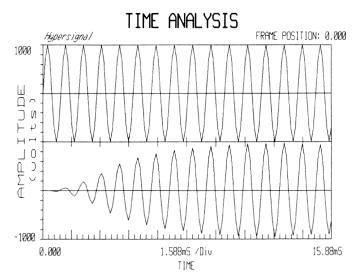

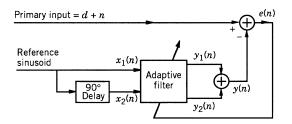

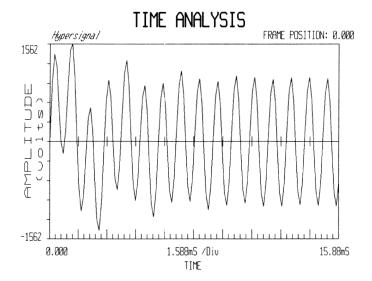

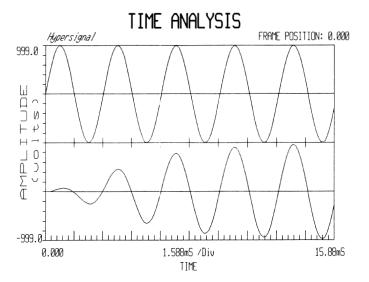

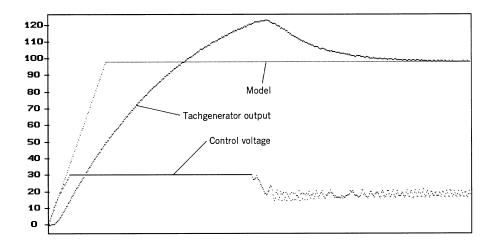

| PASS2B          | COF    | 1083   | FFT8C           | OUT   | 5837  |